News and Press

Leveraging fast process modeling for assessing GAA standard cells

2025 Symposium on VLSI Technology and Circuits

EricPanning, Sreekar Bathula,

Paul Gutwin, Ayush Gupta, Swapnil Tembhare, H.Wong, Gerhard Rzepa, Christian Schleich

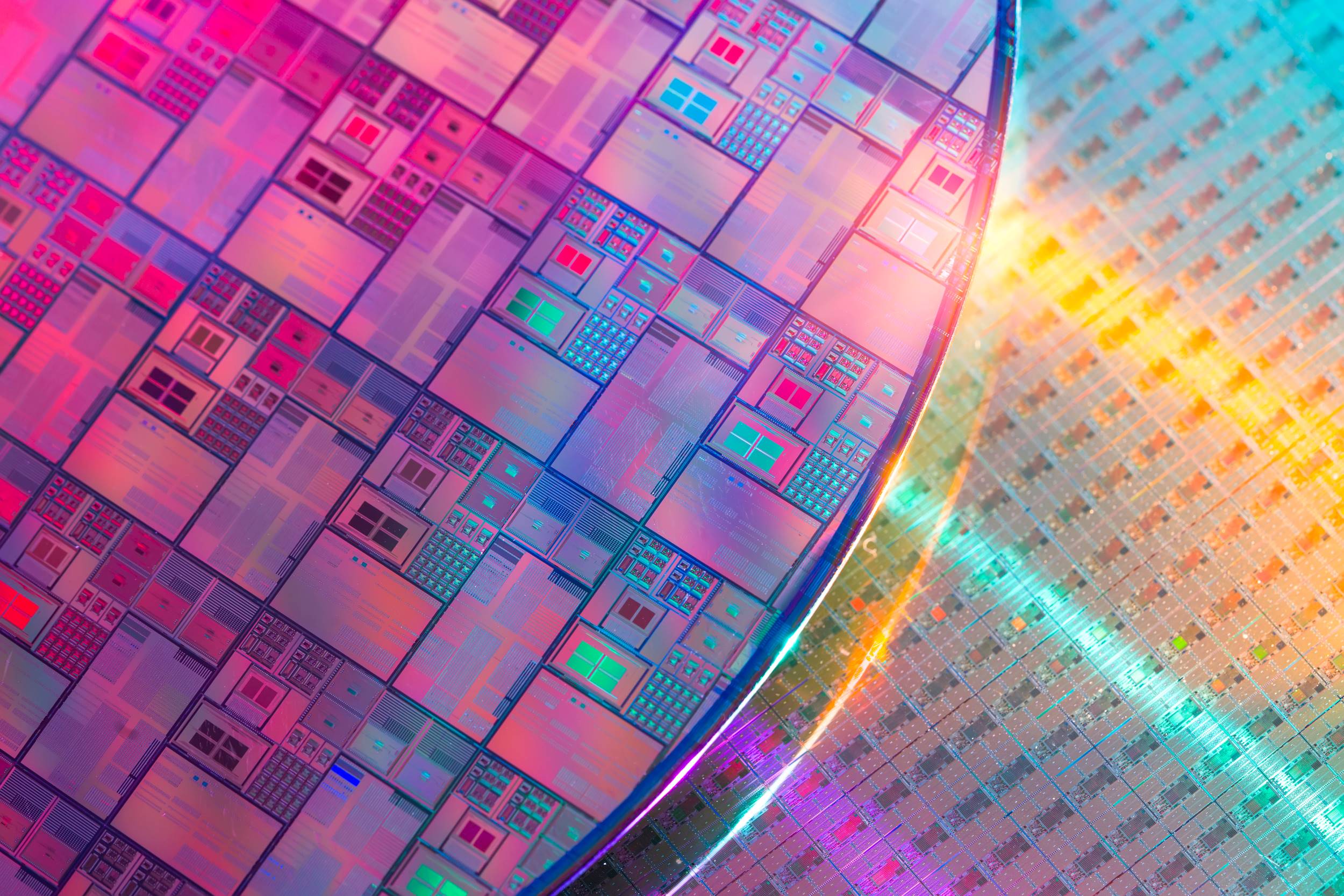

DTCO 2.0: GenChip Approach to Standard Cell Optimization

- Flexible solutions for current and future process technologies

- Process sensitivity analysis

- Electrical characterization

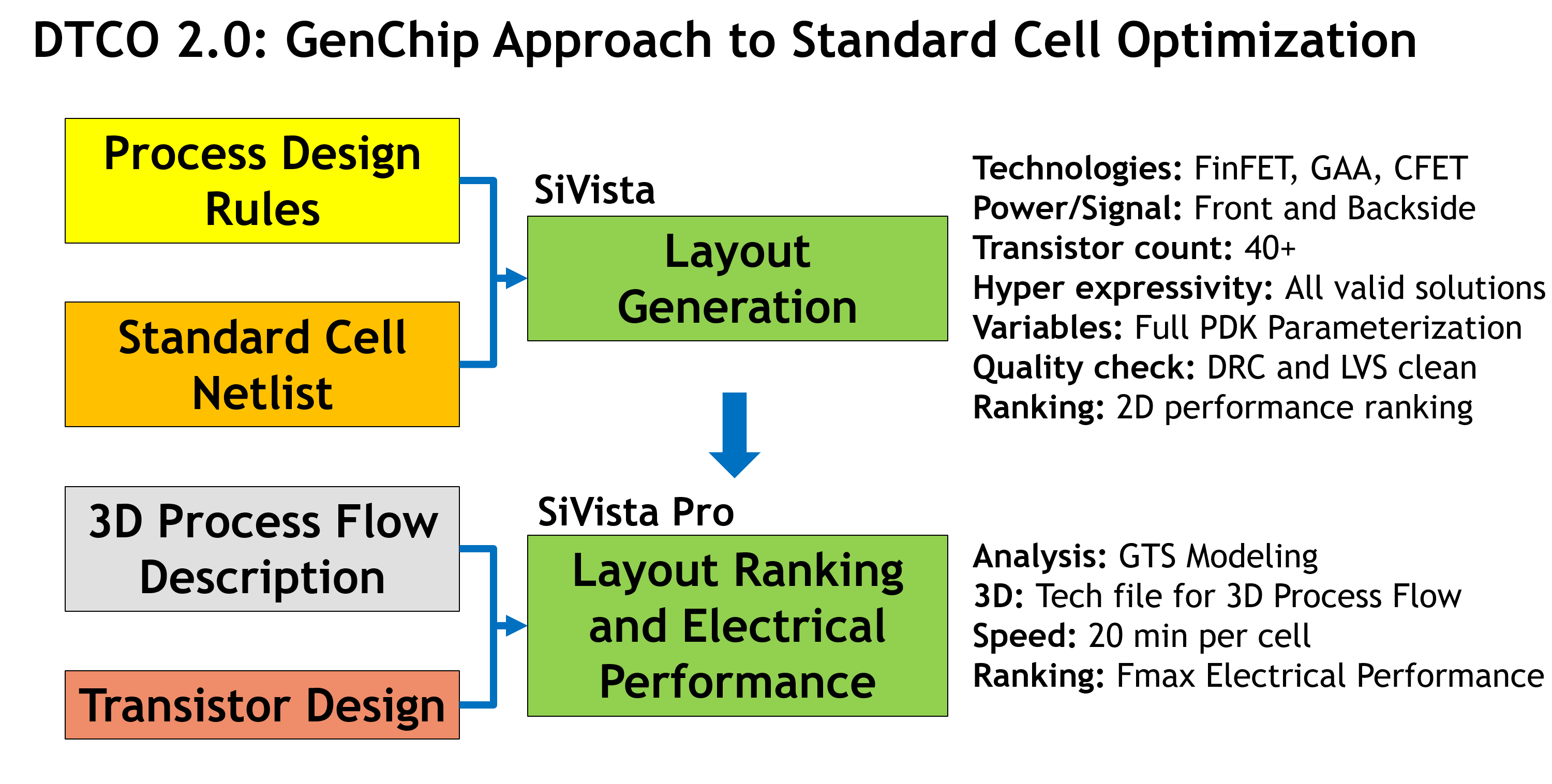

INVD4 performance on a GAA A14 node

- High speed parametric studies

- Transistor level netlist optimization

- Flexible design rules

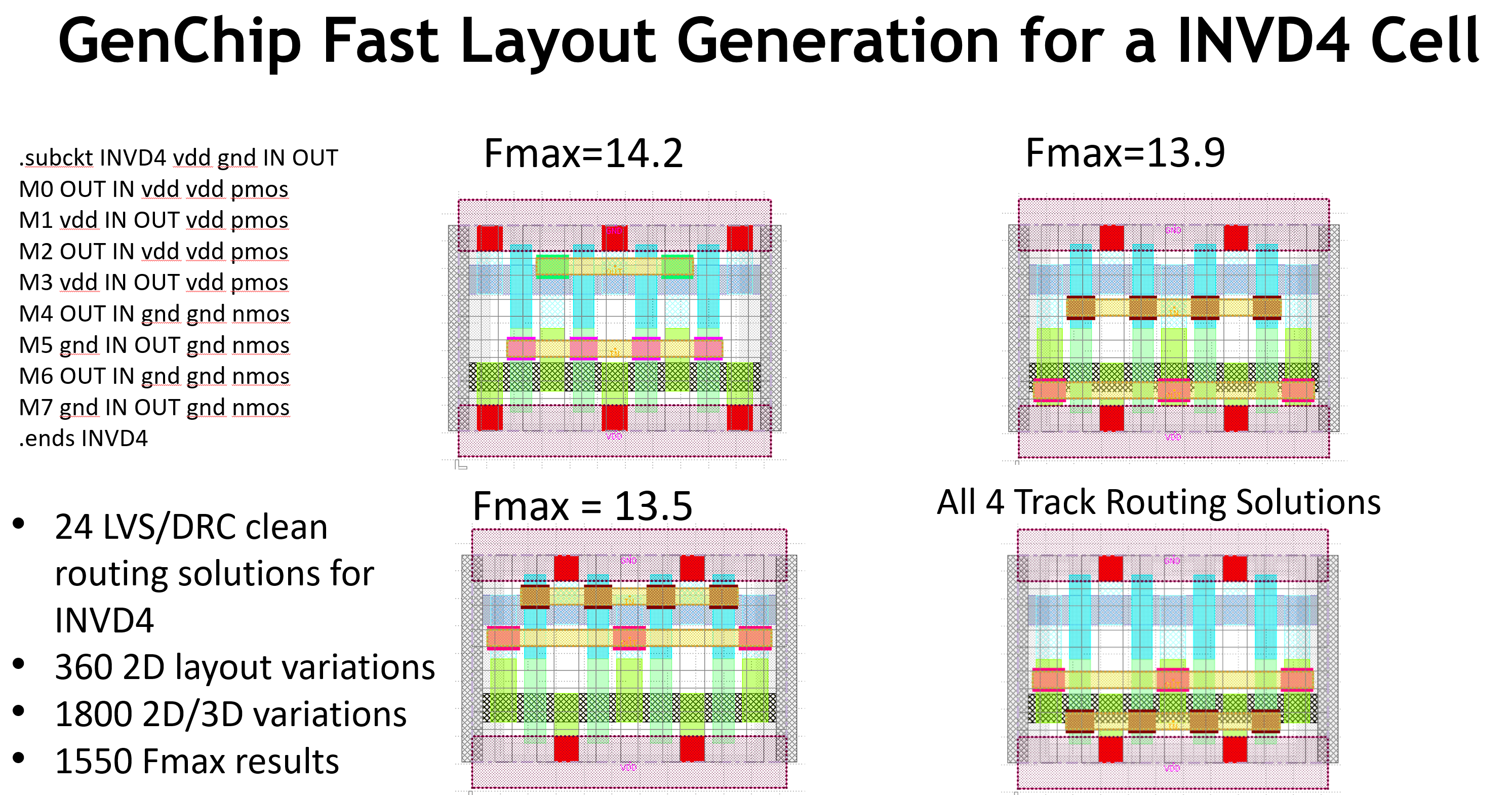

GenChip Fast Layout Generation for a INVD4 Cell

- Example of optimizing an inverter standard cell

- Routing and performance optimization

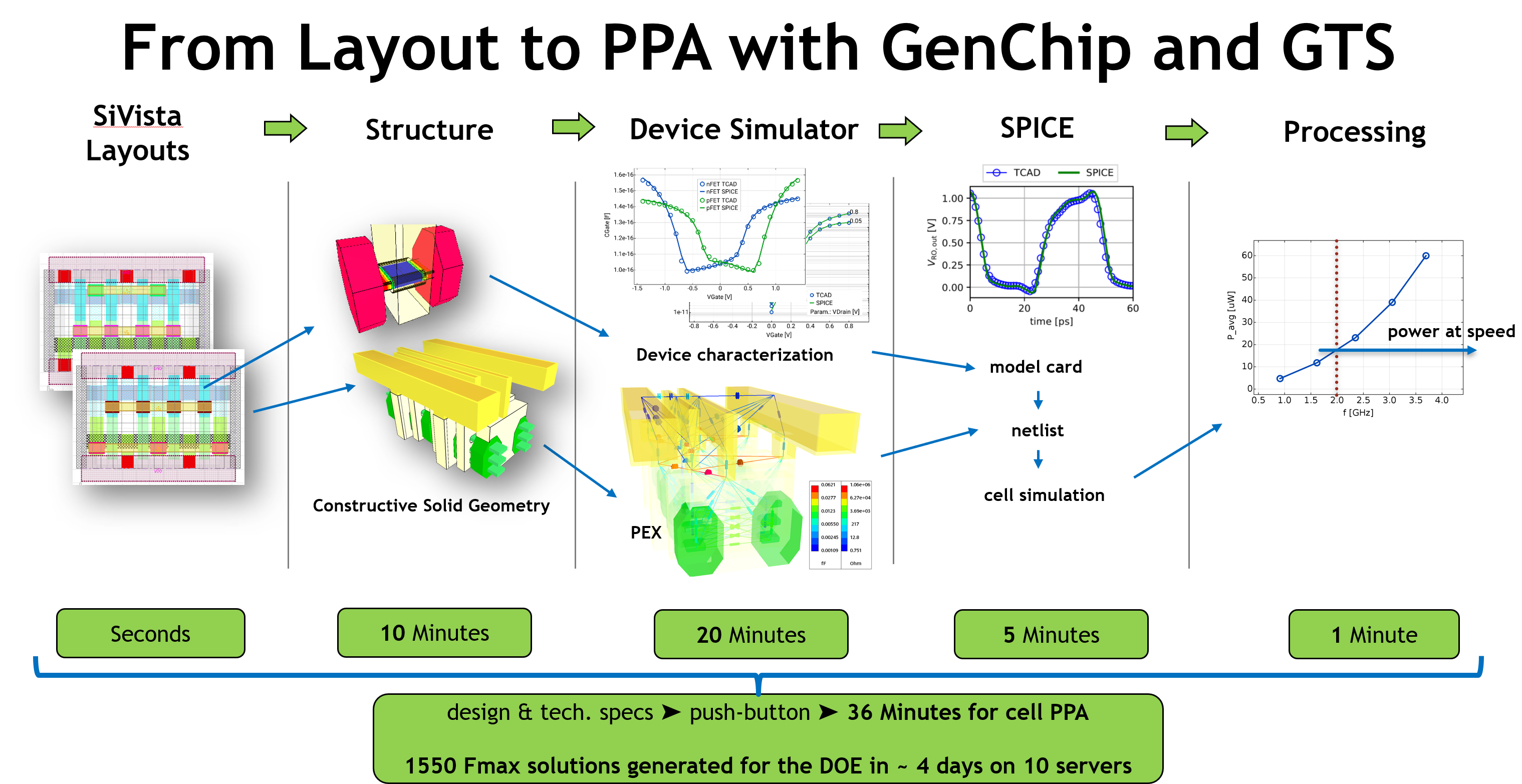

From Layout to PPA with GenChip and GTS

- Full characterization loop for electrical analysis

- Highspeed enables deep permutations

- Performance and Yield

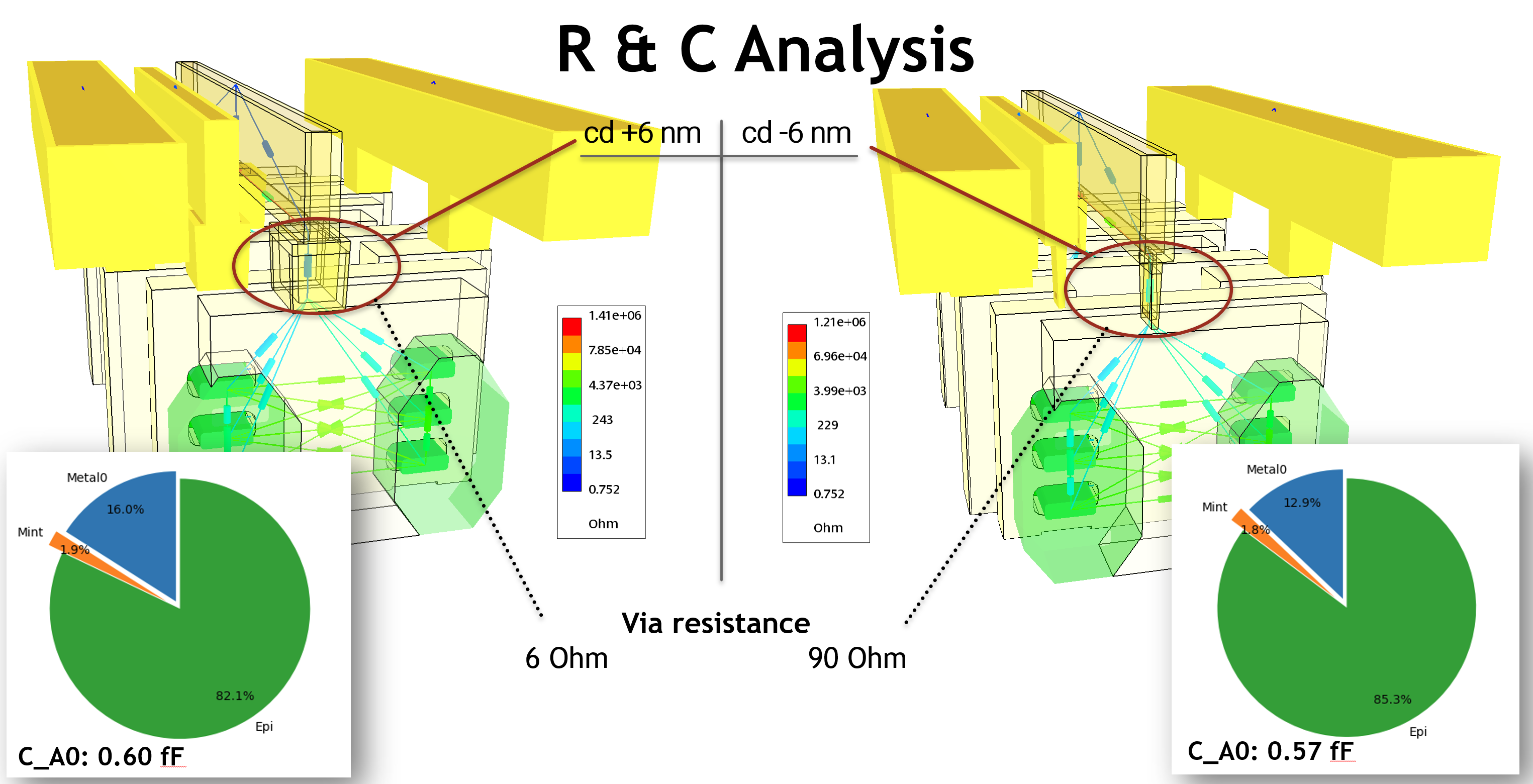

R & C Analysis

- Electrical impact of Via CD variation

- 3D visualization of variability

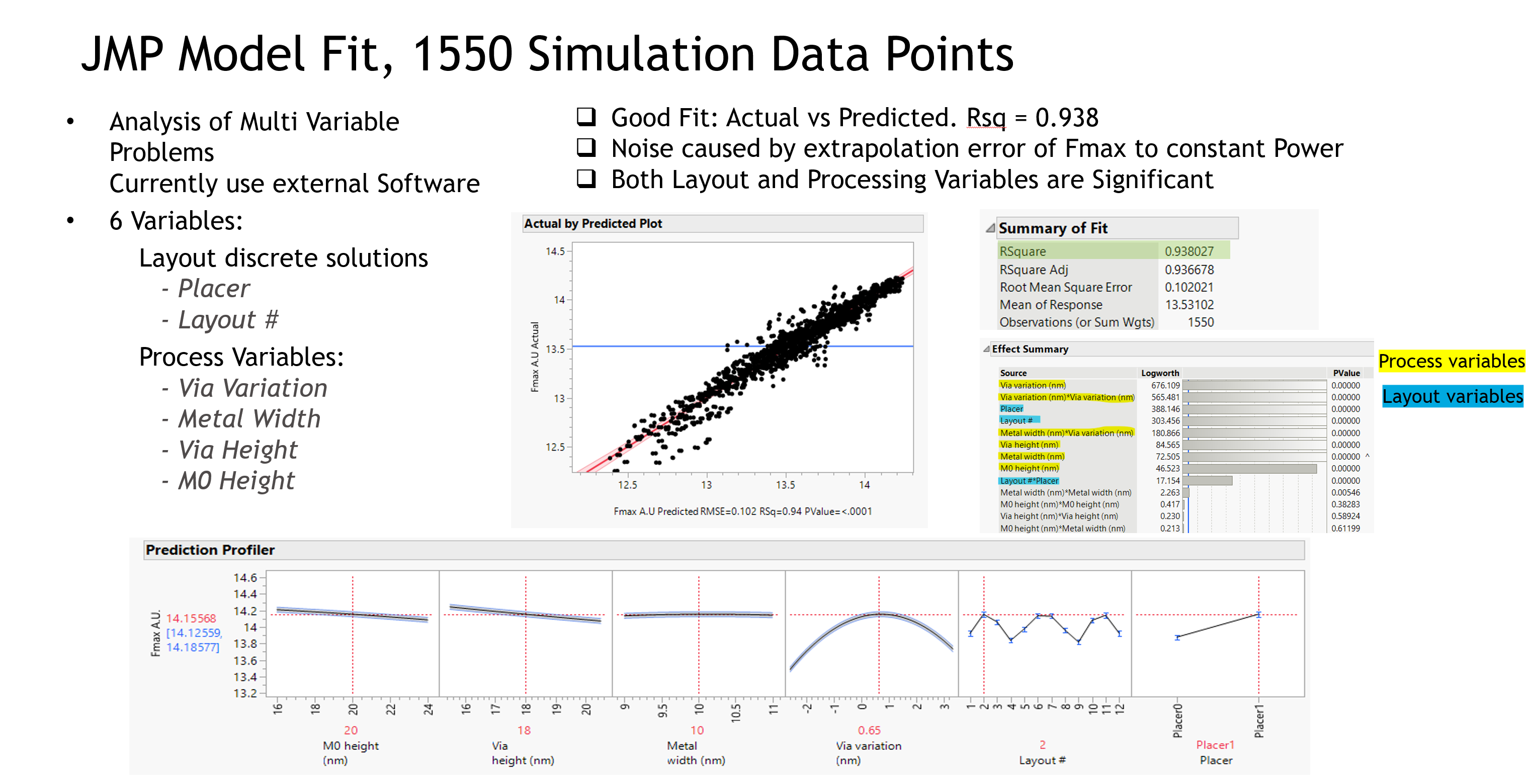

JMP Model Fit, 1550 Simulation Data Points

- Good model fit in JMP for 1550 simulation points

- Via variation dominates for process Fmax

- Variations in layout 2ndmost important distinction

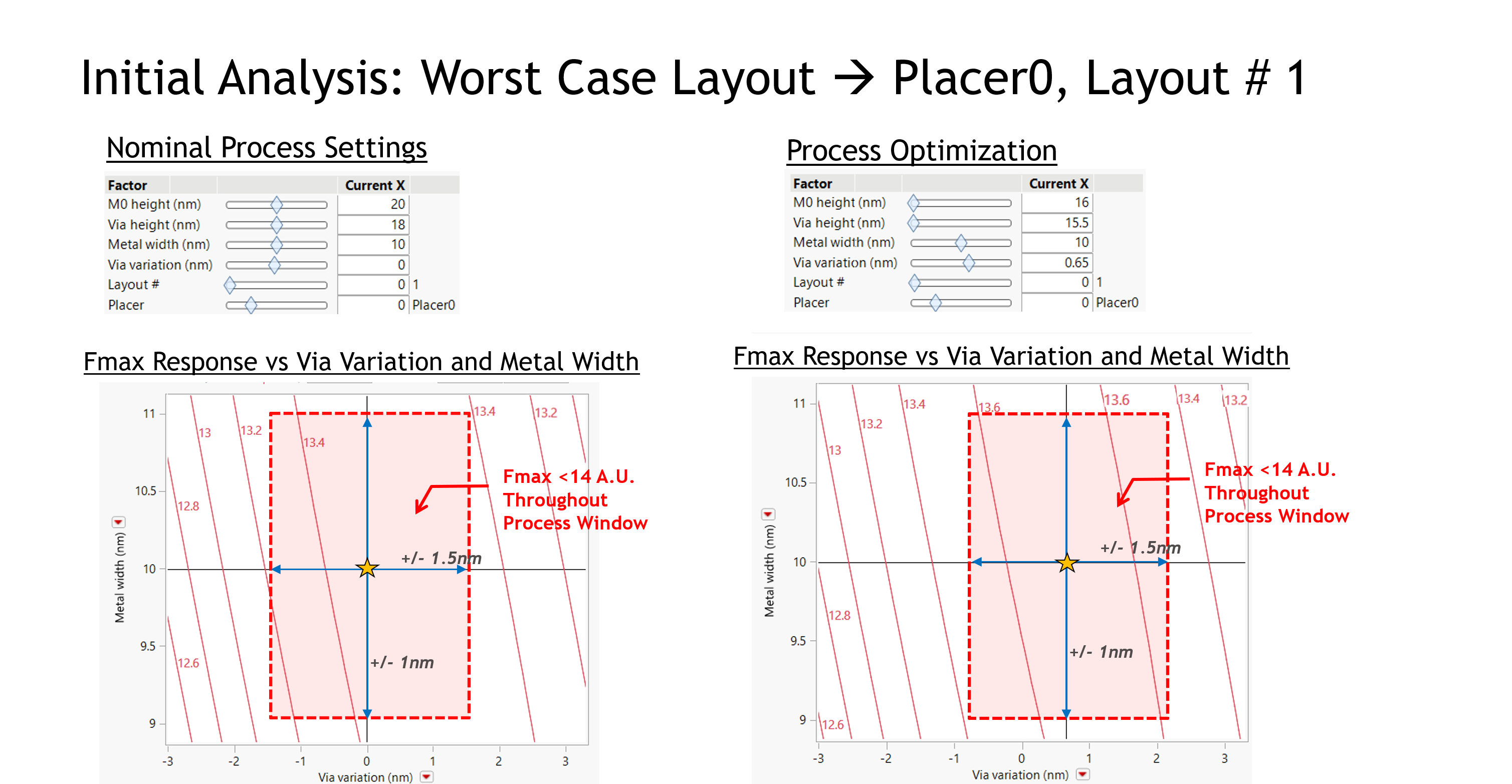

Initial Analysis: Worst Case Layout à Placer0, Layout # 1

- Non-ideal cell layout impacts performance potential

- Process improvement cannot overcome layout consequences

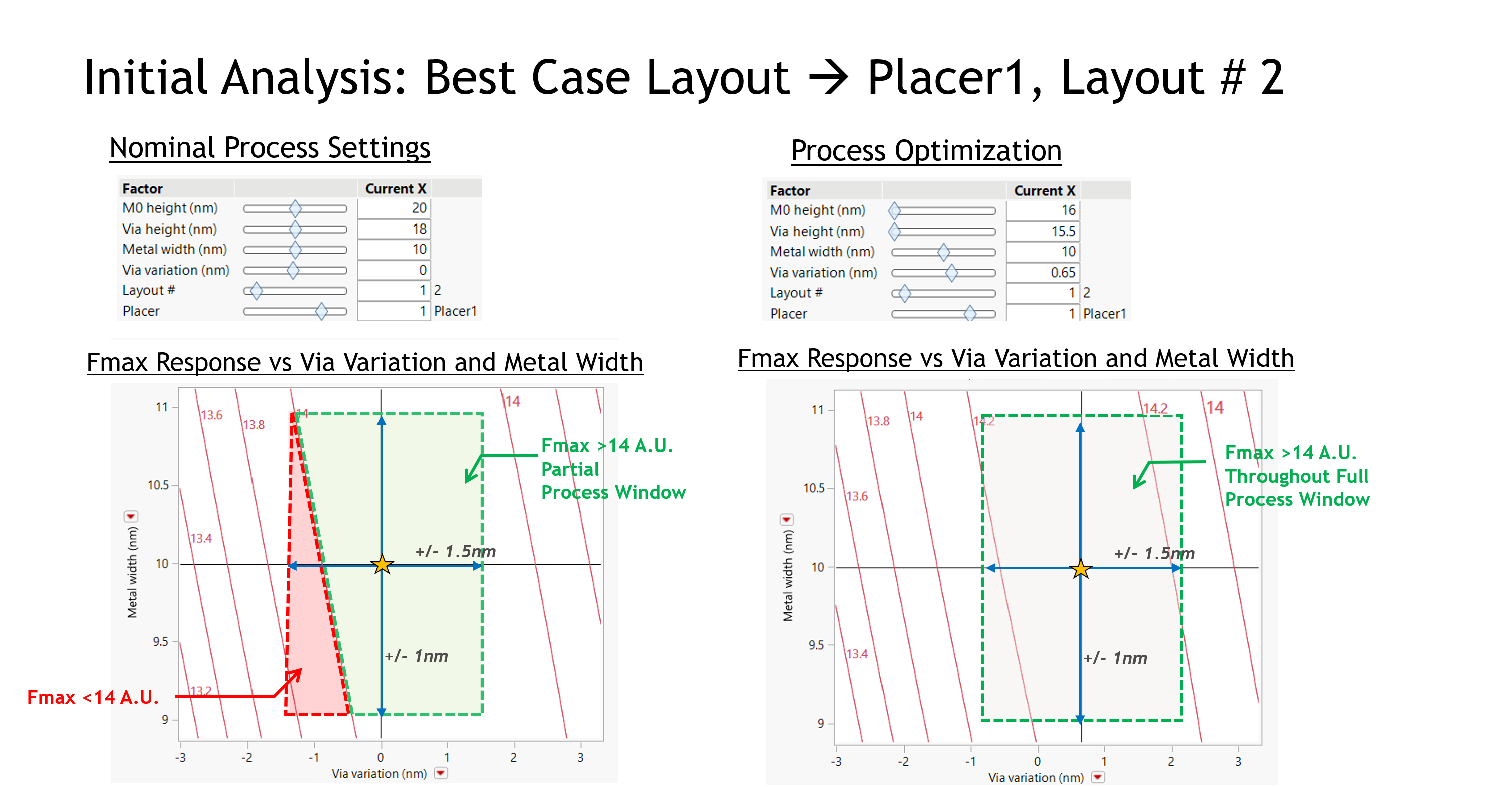

Initial Analysis: Best Case Layout à Placer1, Layout # 2

- Co-optimizing layout and process center delivers highest performing and most robust cell design

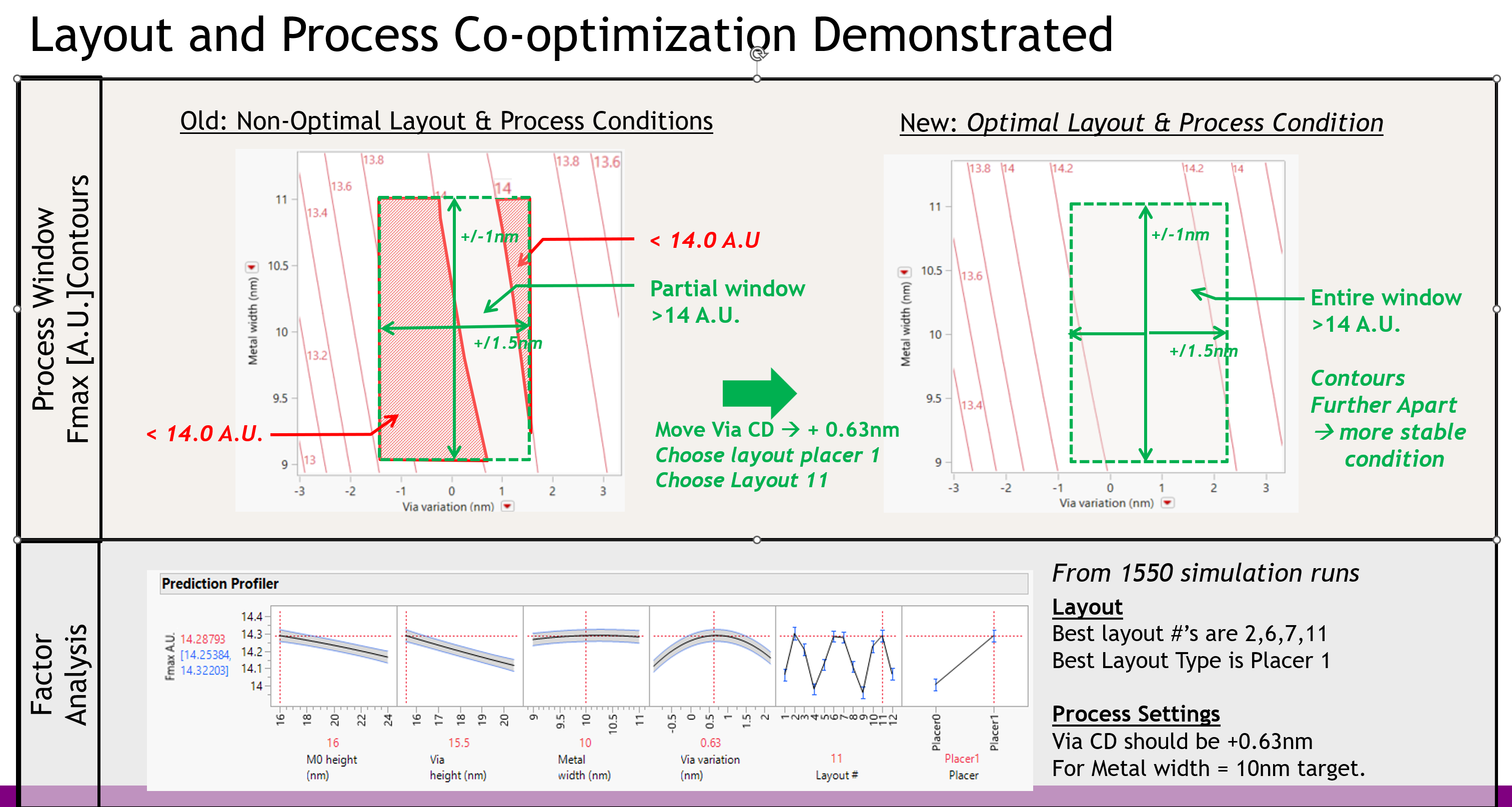

Layout and Process Co-optimization Demonstrated

- Co-optimization of layout and process center essential for optimum performance

- Expanding this work to more complex cells and advanced nodes

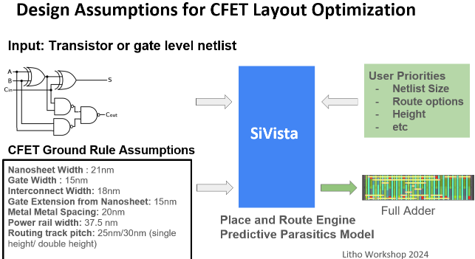

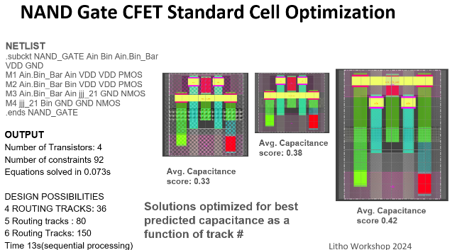

Co-optimization of Standard Cells for CFET Technology

LITHO WORKSHOP 2024

Rancho Bernardo, CA

Sreekar Bathula, Eric Panning, H.Wong, Swapnil Tembhare

GenChip solutions optimize layouts by processing gate level netlists and process design rules.

In this study, a CFET architecture was examined with a CFET appropriate ground rule assumptions.

GenChip software identifies layout solutions as well as ranks solutions by predicted electrical performance

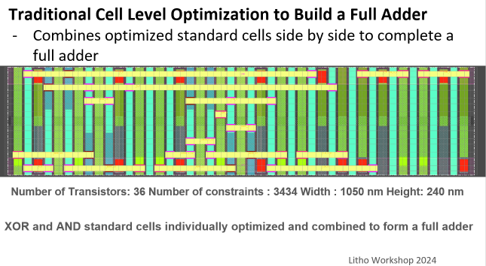

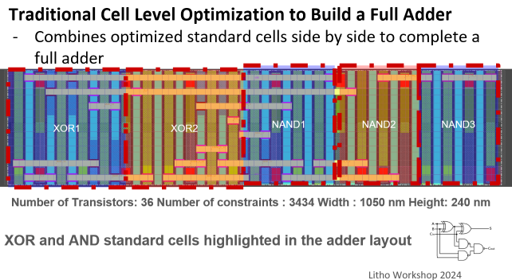

This is a traditional approach for building a full adder based on XOR and NAND Standard cells

The color highlighted regions show the standard cells used to build a full adder

GenChip software can process high density standard cells holistically for area savings and performance.

20% area improvement demonstrated

Discover Our Cutting-Edge Technology

Contact us for more information or to schedule a demonstration.